TLV320AIC3262

ZHCSE78A - DECEMBER 2011 - REVISED SEPTEMBER 2015

# TLV320AlC3262 具有 miniDSP、DirectPath 耳机和立体声 D 类扬声器放大器的超低功耗立体声音频编解码器

## 1 特性

- 信噪比 (SNR) 为 101dB 的立体声音频数模转换器 (DAC)

- 2.7mW 立体声 48kHz DAC 播放

- SNR 为 93dB 的立体声音频模数转换器 (ADC)

- 5.6mW 立体声 48kHz ADC 录制

- 8kHz 至 192kHz 播放和录制

- 30mW DirectPath<sup>TM</sup> 耳机驱动器免除了对较大输出 隔直电容器的需要

- 128mW 差分接收器输出驱动器

- 立体声 D 类扬声器驱动器

- -1.7W (8 $\Omega$ , 5.5V, 10% THDN)

- 1.4W (8Ω, 5.5V, 1% THDN)

- 立体声线路输出

- PowerTune™- 调节功率与SNR 的关系

- 扩展信号处理选项

- 8个单端或4个全差分模拟输入

- 立体声数字和模拟麦克风输入

- 低功耗模拟旁路模式

- 异步采样率转换

- 支持 PurePath™Studio 的完全可编程增强型 miniDSP

- 支持语音和音频 应用的扩展算法

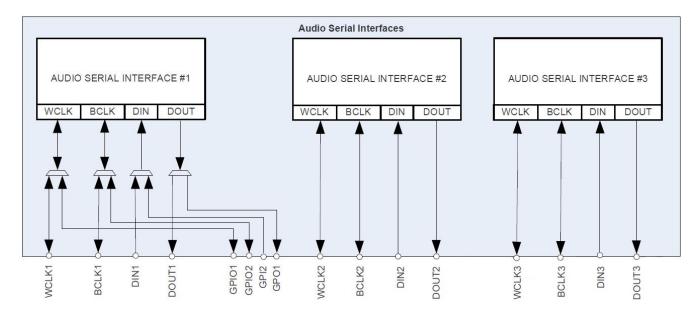

- 三个独立数字音频串行接口

- 所有音频串行接口支持时分复用 (TDM) 和单声 道脉冲编码调制 (PCM)

- 音频串行接口 1 提供 8 通道输入和输出

- 可编程锁相环 (PLL) 以及低频计时

- 可编程 12 位逐次逼近 (SAR) ADC

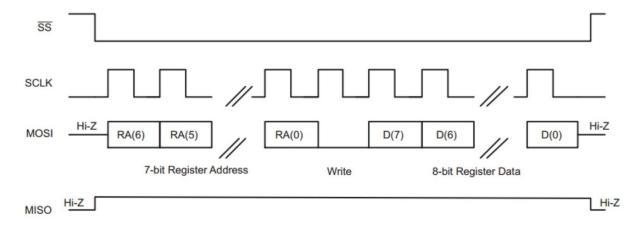

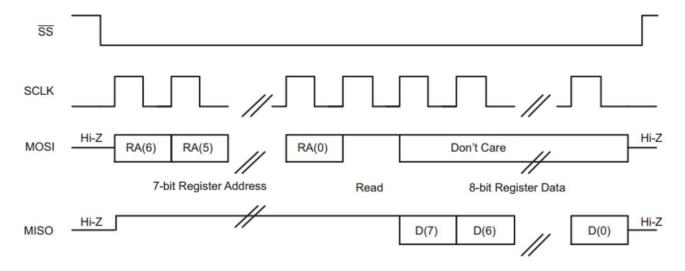

- SPI 和 I<sup>2</sup>C 控制接口

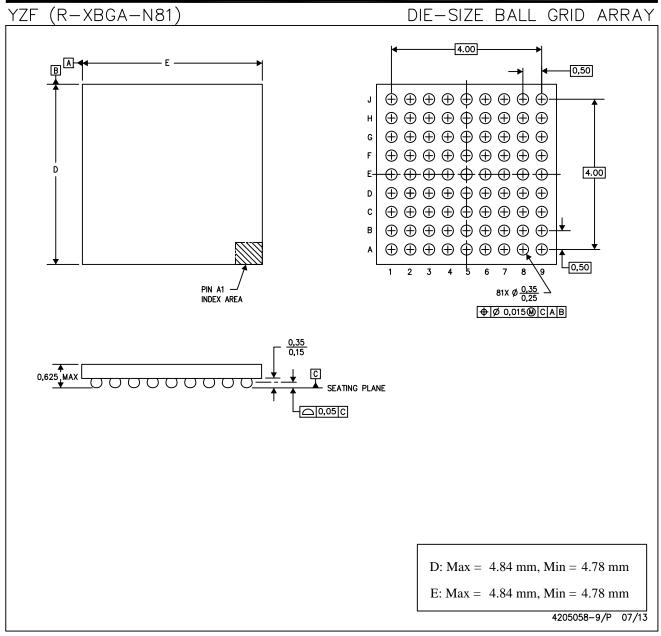

- 4.81mm x 4.81mm x 0.625mm 81 焊球晶圆级芯片 (WCSP) (YZF) 封装

## 2 应用范围

- 移动手持机

- 平板电脑和电子书

- 便携式导航设备 (PND)

- 便携式媒体播放器 (PMP)

- 便携式游戏系统

- 便携式计算机

- 噪声抑制 (NS)

- 扬声器保护

- 高级数字信号处理 (DSP) 算法

#### 3 说明

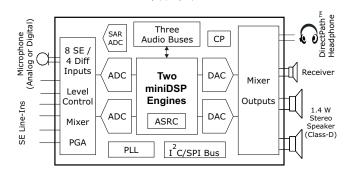

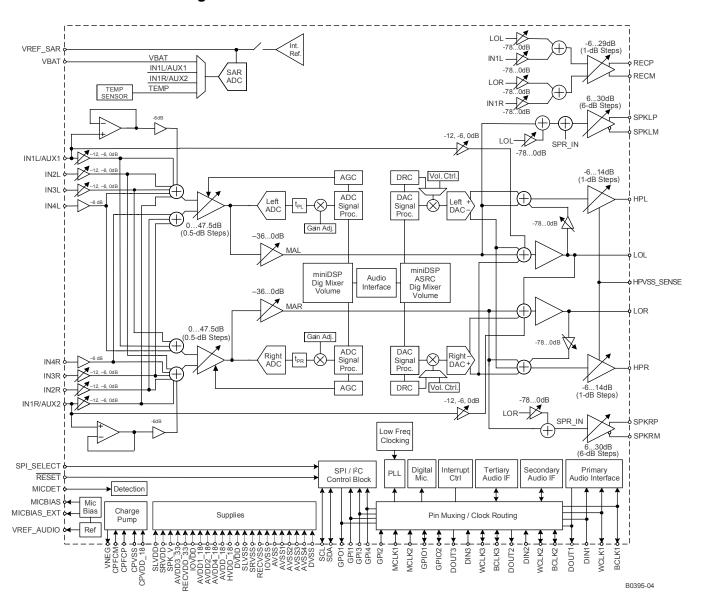

TLV320AIC3262(也称为 AIC3262)是一款灵活的高集成度、低功耗、低电压立体声音频编解码器。

AIC3262 具有 数字麦克风输入和可编程输出、

PowerTune 功能、 enhanced fully-programmable miniDSP, 预定义和参数化的信号处理模块、集成 PLL 和灵活的音频接口。凭借大量基于寄存器的控制(受控对象包括功率、输入和输出通道配置、增益、音效、引脚多路复用和时钟等),该器件能够精确满足其应用的要求。

#### 器件信息(1)

| 器件型号          | 封装         | 封装尺寸 (标称值)      |

|---------------|------------|-----------------|

| TLV320AIC3262 | DSBGA (81) | 4.81mm x 4.81mm |

(1) 要了解所有可用封装,请见数据表末尾的可订购产品附录。

#### 简化框图

| $\neg$ | $\rightarrow$ |

|--------|---------------|

| -      | ملب           |

| _      |               |

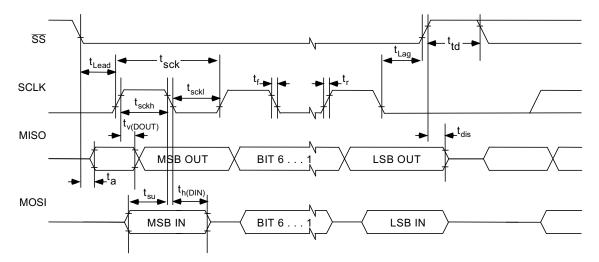

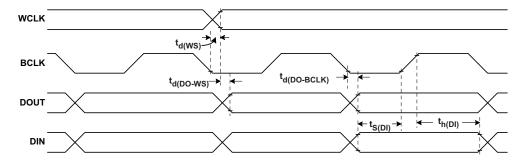

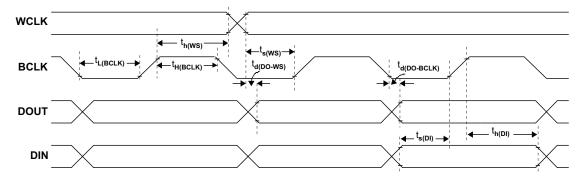

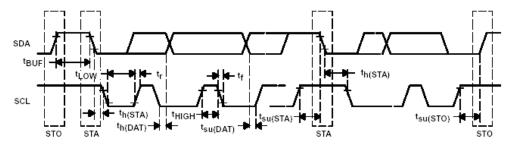

| 1 | 特性                                                                                                       |    | 8.16 I <sup>2</sup> C Interface Timing (see Figure 6) | 25         |

|---|----------------------------------------------------------------------------------------------------------|----|-------------------------------------------------------|------------|

| 2 | 应用范围 1                                                                                                   |    | 8.17 SPI Interface Timing                             | 25         |

| 3 | 说明                                                                                                       |    | 8.18 Dissipation Ratings                              | 26         |

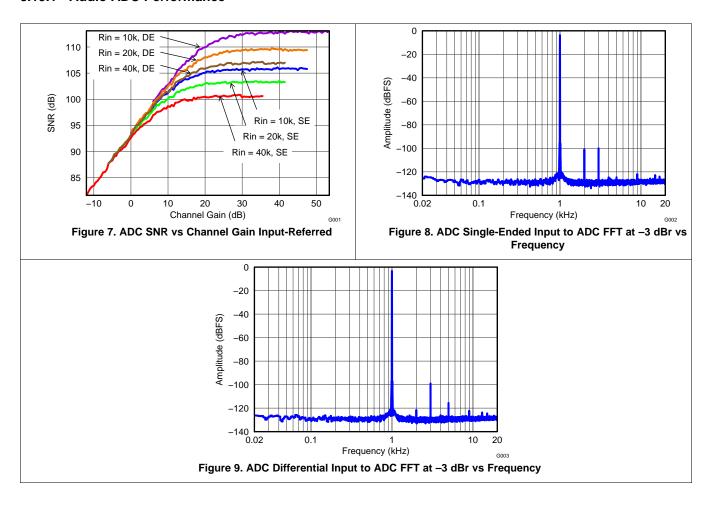

| 4 | 修订历史记录                                                                                                   |    | 8.19 Typical Characteristics                          | 28         |

| 5 | 说明(续)3                                                                                                   | 9  | Parameter Measurement Information                     | 31         |

| 6 | Device Comparison Table                                                                                  | 10 | Detailed Description                                  | 32         |

| 7 |                                                                                                          |    | 10.1 Overview                                         |            |

| - | Pin Configuration and Functions                                                                          |    | 10.2 Functional Block Diagram                         | 33         |

| 8 | Specifications 12                                                                                        |    | 10.3 Feature Description                              |            |

|   | 8.1 Absolute Maximum Ratings                                                                             |    | 10.4 Device Functional Modes                          | 59         |

|   | 8.2 ESD Ratings                                                                                          |    | 10.5 Register Maps                                    | 60         |

|   | 8.3 Recommended Operating Conditions                                                                     | 11 | Application and Implementation                        | <b>7</b> 0 |

|   | 8.4 Thermal Information                                                                                  |    | 11.1 Application Information                          |            |

|   | 8.5 Electrical Characteristics, SAR ADC                                                                  |    | 11.2 Typical Application                              | 71         |

|   | 8.6 Electrical Characteristics, ADC                                                                      | 12 | Power Supply Recommendations                          |            |

|   | 8.7 Electrical Characteristics, Bypass Outputs                                                           |    | 12.1 Device Power Consumption                         |            |

|   | • •                                                                                                      | 13 | Layout                                                | 75         |

|   | 8.9 Electrical Characteristics, Audio DAC Outputs 19 8.10 Electrical Characteristics, Class-D Outputs 22 |    | 13.1 Layout Guidelines                                |            |

|   | 8.11 Electrical Characteristics, Miscellaneous                                                           |    | 13.2 Layout Examples                                  | 75         |

|   | 8.12 Electrical Characteristics, Miscellaneous                                                           | 14 | 器件和文档支持                                               | <b>7</b> 8 |

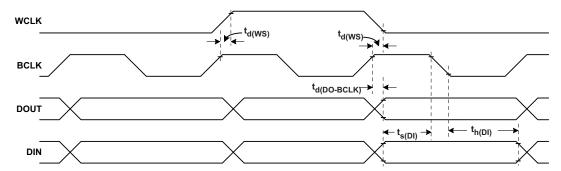

|   | 8.13 I <sup>2</sup> S/LJF/RJF Timing in Master Mode (see                                                 |    | 14.1 文档支持                                             |            |

|   | Figure 2)                                                                                                |    | 14.2 社区资源                                             | 78         |

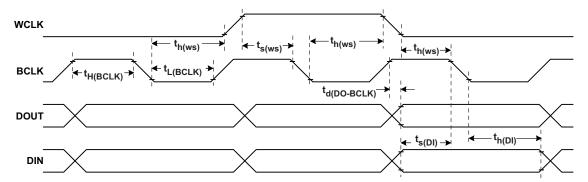

|   | 8.14 I <sup>2</sup> S/LJF/RJF Timing in Slave Mode (see                                                  |    | 14.3 商标                                               |            |

|   | Figure 3)24                                                                                              |    | 14.4 静电放电警告                                           | 78         |

|   | 8.15 DSP/Mono PCM Timing in Slave Mode (see                                                              |    | 14.5 Glossary                                         | 78         |

|   | Figure 5) 24                                                                                             | 15 | 机械、封装和可订购信息                                           |            |

|   |                                                                                                          | 13 | 小小风、                                                  |            |

# 4 修订历史记录

注: 之前版本的页码可能与当前版本有所不同。

#### Changes from Original (December 2011) to Revision A

**Page**

#### 5 说明 (续)

TLV320AIC3262 具有 两个完全可编程的 miniDSP 内核,支持器件的录制和/或播放路径中的应用特定算法。 miniDSP 内核完全由软件编程。目标 miniDSP 算法(如噪声抑制或高级 DSP 滤波)在上电后载入器件。

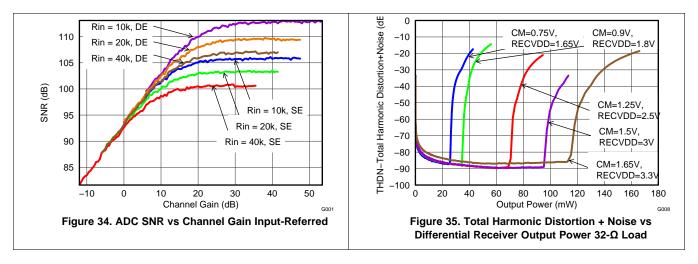

该器件与先进的 PowerTune 技术相结合,可支持从 8kHz 单声道语音播放到 192kHz DAC 播放的运行,因此非常适用于便携式电池供电类音频和电话通讯 应用。

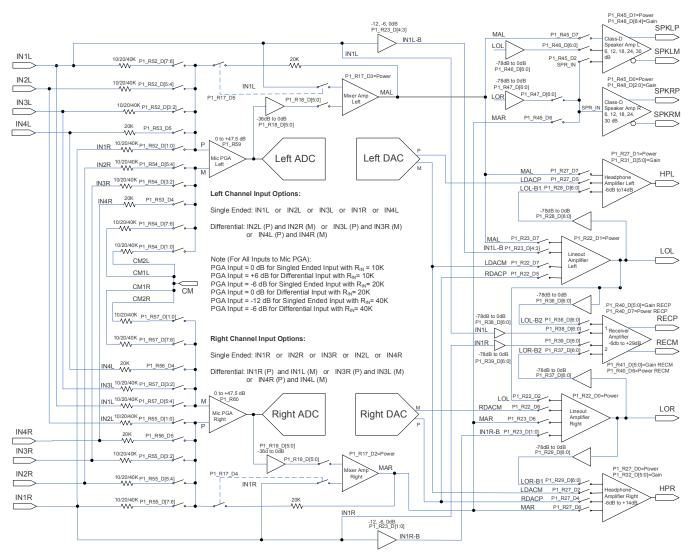

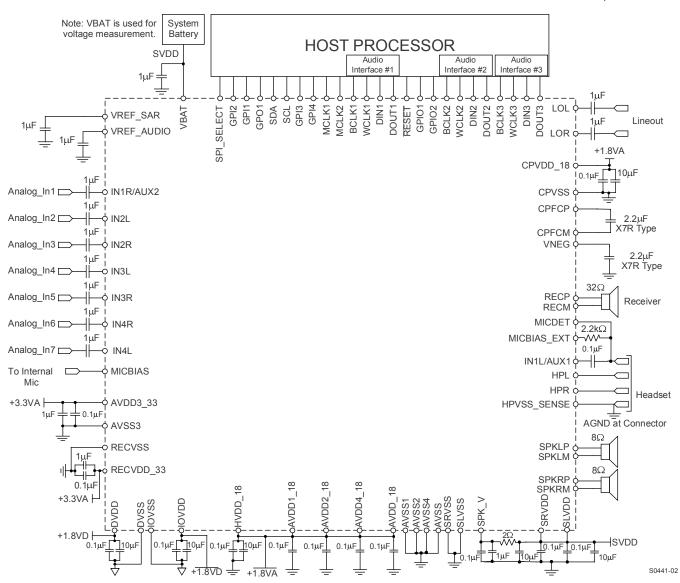

TLV320AlC3262 的录制路径支持从 8kHz 单声道至 192kHz 立体声的录制并包含可编程输入通道配置。该配置涵盖单端和差分设置以及输入信号的悬空或混合。录制路径还提供了一个以数字方式控制的立体声麦克风前置放大器以及集成麦克风偏置。数字信号处理模块的一项应用是移除可由机械耦合(例如数码相机的光学变焦)引入的可闻性噪声。录制路径也可配置为立体声数字麦克风脉冲密度调制 (PDM) 接口,该接口通常在 64 Fs 或 128 Fs 的条件下使用。

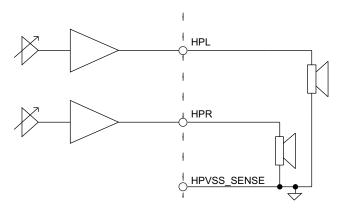

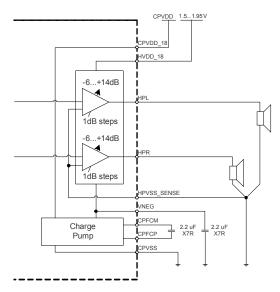

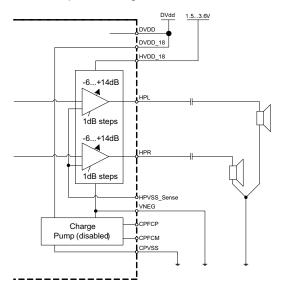

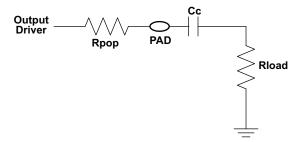

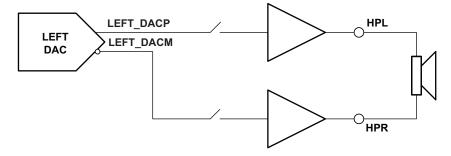

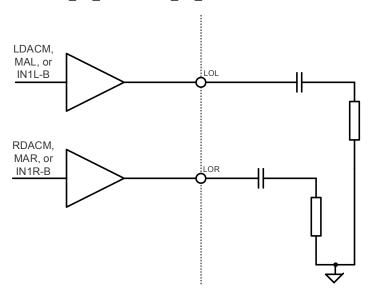

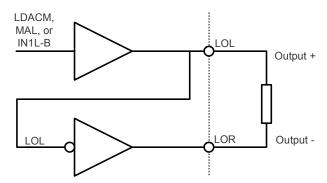

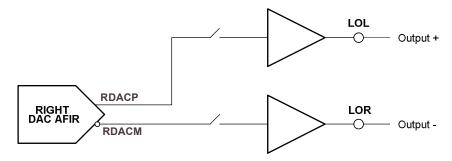

播放路径提供了用于滤波和音效的信号处理模块以及耳机、线路、接收器和 D 类扬声器输出,支持对 DAC 和模拟输入信号的灵活混合以及可编程音量控制。播放路径包含两个高功率 DirectPath<sup>TM</sup> 耳机输出驱动器,免除了对于交流耦合电容的需要。内置的电荷泵为中心接地的头戴式耳机驱动器生成负电源。此类耳机输出驱动器可以多种方式进行配置,包括立体声和单声道桥接式负载 (BTL)。此外,播放音频可传递至集成的立体声 D 类扬声器驱动器或差分接收器放大器。

借助集成的 PowerTune 技术,该器件可调节至正确的功耗-性能平衡点。在移动环境中 使用时, 移动应用经常需要在低功耗状态下运行。在音频坞环境中使用时,与功耗问题相比,最大限度地降低噪声才是关注的重点。借助 PowerTune,TLV320AlC3262 能够同时满足上述两种情况。

TLV320AIC3262 所需的内部时钟可能来自多个源,包括 MCLK1 引脚、MCLK2 引脚、BCLK1 引脚、BCLK2 引脚、几个通用 I/O 引脚或内部 PLL 输出,PLL 的输入也来源于相似引脚。虽然内置的分数 PLL 能够确保获得适合的时钟信号,但 TI 建议不要将其用于最低功率设置。PLL 高度可编程,能够接受频率范围为 512kHz 至 50MHz 的可用输入时钟。要启用更低的时钟频率,集成的低频时钟倍频器也可以用作 PLL 的输入。

TLV320AIC3262 具有一个 12 位逐次逼近寄存器 (SAR) ADC 转换器,支持测量系统电压。这些系统电压测量可能来源于三个专用模拟输入(IN1L/AUX1、IN1R/AUX2 或 VBAT 引脚)或可由 SAR ADC 读取的片上温度传感器。

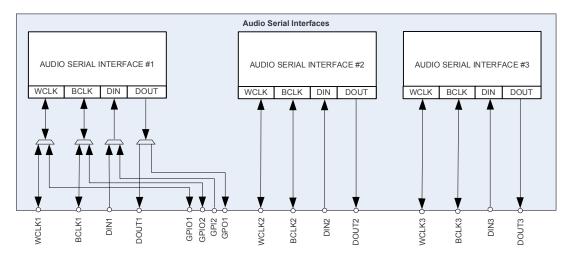

TLV320AlC3262 还 具备 三个完全数字音频串行接口。每个接口支持 I2S、DSP/TDM、RJF、LJF 和单声道 PCM 格式。这使得三条同步音频播放和录制路径成为三条独立的数字音频总线或三块独立的数字音频芯片。此外,通用中断引脚可用于连接第四条数字音频总线,允许终端系统由第四条音频总线轻松切换至三个数字音频串行接口中的任意一个。

该器件采用 4.81 mm x 4.81 mm x 0.625 mm 81-Ball WCSP (YZF) package 封装。

# 6 Device Comparison Table

| PARAMETRICS                           | TLV320AIC3212              | TLV320AIC3262              | TLV320AIC3268              | TLV320AIC3204         | TLV320AIC3254      |

|---------------------------------------|----------------------------|----------------------------|----------------------------|-----------------------|--------------------|

| DACs (number)                         | 2                          | 2                          | 2                          | 2                     | 2                  |

| ADCs (number)                         | 2                          | 2                          | 2                          | 2                     | 2                  |

| Number of Inputs / Number of Outputs  | 8/7                        | 8/7                        | 8/7                        | 6/4                   | 6/4                |

| Resolution (Bits)                     | 16, 20, 24, 32             | 16, 20, 24, 32             | 16, 20, 24, 32             | 16, 20, 24, 32        | 16, 20, 24, 32     |

| Control Interface                     | I2C, SPI                   | I2C, SPI                   | I2C, SPI                   | I2C, SPI              | I2C, SPI           |

| Digital Audio Interface               | I2S, TDM, DSP,<br>L&R, PCM | I2S, TDM, DSP,<br>L&R, PCM | I2S, TDM, DSP,<br>L&R, PCM | I2S, TDM, DSP,<br>L&R | I2S, TDM, DSP, L&R |

| Number of Digital Audio<br>Interfaces | 3                          | 3                          | 3                          | 1                     | 1                  |

| Speaker Amplifier Type                | Class-D                    | Class-D                    | Class-D                    | _                     | _                  |

| Configurable miniDSP                  | No                         | Yes                        | Yes                        | No                    | Yes                |

| Headphone Driver                      | Yes                        | Yes                        | Yes                        | Yes                   | Yes                |

# 7 Pin Configuration and Functions

YZF Package 81-Pin DSBGA Top View

| F V       | VBAT  SPKRP  SRVDD  SPKRM  SLVSS | SPK_V SRVSS SPKLM SLVDD | GPI4  DVSS  LOR  AVDD4_18  CPFCP  CPVDD_18 | GPI2  AVSS2  HPVSS _SENSE  LOL  CPVSS | GPI3  AVSS3  IN4R  AVDD2_18  HPL  VNEG | DVSS  AVSS1  IN1R/AUX2  MICBIAS  HVDD_18 | AVDD_18  AVSS  IN1L/AUX1  MICBIAS _EXT  RECM  RECVDD_33 | IN2R  IN3L  VREF_SAR  AVDD1_18  RECP | IN2L IN3R VREF_AUDIO IN4L MICDET |

|-----------|----------------------------------|-------------------------|--------------------------------------------|---------------------------------------|----------------------------------------|------------------------------------------|---------------------------------------------------------|--------------------------------------|----------------------------------|

| E SI D SI | VBAT SPKRP SRVDD                 | SPK_V SRVSS             | DVSS  LOR  AVDD4_18                        | AVSS2  HPVSS _SENSE  LOL              | AVSS3 IN4R AVDD2_18                    | AVSS1 IN1R/AUX2 MICBIAS                  | AVSS  IN1L/AUX1  MICBIAS _EXT                           | IN3L  VREF_SAR  AVDD1_18             | IN2L IN3R VREF_AUDIO             |

| F V       | VBAT  SPKRP  SRVDD               | SPK_V SRVSS             | DVSS                                       | AVSS2  HPVSS _SENSE                   | AVSS3                                  | AVSS1                                    | AVSS IN1L/AUX1 MICBIAS                                  | IN3L<br>VREF_SAR                     | IN3R  VREF _AUDIO                |

| F \       | VBAT                             | IOVSS SPK_V             | DVSS                                       | AVSS2                                 | AVSS3                                  | AVSS1                                    | AVSS                                                    | IN3L                                 | IN2L<br>IN3R                     |

| F         | VBAT                             | IOVSS                   |                                            |                                       |                                        |                                          |                                                         |                                      | IN2L                             |

|           |                                  |                         | GPI4                                       | GPI2                                  | GPI3                                   | DVSS                                     | AVDD_18                                                 | IN2R                                 |                                  |

| G M       | MCLK2                            | RESET                   |                                            |                                       |                                        |                                          |                                                         |                                      | MCLK1                            |

|           |                                  |                         | SPI_SELECT                                 | DIN3                                  | WCLK3                                  | WCLK2                                    | DIN2                                                    | BCLK2                                |                                  |

| н         | OVDD                             | GPIO2                   | BCLK3                                      | GPO1                                  | SDA                                    | SCL                                      | IOVDD                                                   | DOUT1                                | BCLK1                            |

| J         | DVDD                             | GPIO1                   | DOUT3                                      | DOUT2                                 | GPI1                                   | IOVSS                                    | DVDD                                                    | WCLK1                                | DIN1                             |

## **Pin Functions**

| Pin Functions PIN |                                                                                                             |                                                                                                                                             |  |  |  |

|-------------------|-------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| T                 | TYPE                                                                                                        | DESCRIPTION                                                                                                                                 |  |  |  |

|                   | P                                                                                                           | 3.3-V Power Supply for Micbias                                                                                                              |  |  |  |

| _                 |                                                                                                             | Receiver Driver Ground                                                                                                                      |  |  |  |

|                   |                                                                                                             | 3.3-V Power Supply for Receiver Driver                                                                                                      |  |  |  |

| _                 |                                                                                                             | Right Headphone Output                                                                                                                      |  |  |  |

|                   |                                                                                                             | Charge Pump Negative Supply                                                                                                                 |  |  |  |

| _                 |                                                                                                             | Charge Pump Flying Capacitor M terminal                                                                                                     |  |  |  |

|                   |                                                                                                             | Power Supply Input for Charge Pump                                                                                                          |  |  |  |

| _                 |                                                                                                             | Analog Ground for Class-D                                                                                                                   |  |  |  |

|                   |                                                                                                             | Left Channel P side Class-D Output                                                                                                          |  |  |  |

|                   |                                                                                                             | Headset Detection Pin                                                                                                                       |  |  |  |

|                   |                                                                                                             | Receiver Driver P Side Output                                                                                                               |  |  |  |

|                   | _                                                                                                           | Receiver Driver M Side Output                                                                                                               |  |  |  |

|                   |                                                                                                             |                                                                                                                                             |  |  |  |

|                   |                                                                                                             | Headphone Amp Power Supply                                                                                                                  |  |  |  |

|                   |                                                                                                             | Left Headphone Output                                                                                                                       |  |  |  |

|                   |                                                                                                             | Charge Pump Ground                                                                                                                          |  |  |  |

|                   |                                                                                                             | Charge Pump Flying Capacitor P Terminal                                                                                                     |  |  |  |

|                   |                                                                                                             | Left Channel Class-D Output Stage Power Supply                                                                                              |  |  |  |

|                   |                                                                                                             | Left Channel Class-D Output Stage Ground                                                                                                    |  |  |  |

|                   |                                                                                                             | Analog Input 4 Left                                                                                                                         |  |  |  |

| _                 |                                                                                                             | 1.8-V Analog Power Supply                                                                                                                   |  |  |  |

| _                 |                                                                                                             | Output Bias Voltage for Headset Microphone.                                                                                                 |  |  |  |

|                   |                                                                                                             | Output Bias Voltage for Microphone to be used for on-board Microphones                                                                      |  |  |  |

|                   |                                                                                                             | 1.8-V Analog Power Supply                                                                                                                   |  |  |  |

|                   |                                                                                                             | Left Line Output                                                                                                                            |  |  |  |

| _                 |                                                                                                             | 1.8-V Analog Power Supply for Class-D                                                                                                       |  |  |  |

|                   | _                                                                                                           | Left Channel M side Class-D Output                                                                                                          |  |  |  |

| SPKRM             | 0                                                                                                           | Right Channel M side Class-D Output                                                                                                         |  |  |  |

| VREF_AUDIO        | 0                                                                                                           | Analog Reference Filter Output                                                                                                              |  |  |  |

| VREF_SAR          | I/O                                                                                                         | SAR ADC Voltage Reference Input or Internal SAR ADC Voltage Reference Bypass Capacitor Pin                                                  |  |  |  |

| IN1L/AUX1         | I                                                                                                           | Analog Input 1 Left, Auxiliary 1 Input to SAR ADC (Special Function: Left Channel High Impedance Input for Capacitive Sensor Measurement)   |  |  |  |

| IN1R/AUX2         | I                                                                                                           | Analog Input 1 Right, Auxiliary 2 Input to SAR ADC (Special Function: Right Channel High Impedance Input for Capacitive Sensor Measurement) |  |  |  |

| IN4R              | I                                                                                                           | Analog Input 4 Right                                                                                                                        |  |  |  |

| HPVSS_SENSE       | I                                                                                                           | Headphone Ground Sense Terminal                                                                                                             |  |  |  |

| LOR               | 0                                                                                                           | Right Line Output                                                                                                                           |  |  |  |

| SRVSS             | Р                                                                                                           | Right Channel Class-D Output Stage Ground                                                                                                   |  |  |  |

| SRVDD             | Р                                                                                                           | Right Channel Class-D Output Stage Power Supply                                                                                             |  |  |  |

| IN3R              | - 1                                                                                                         | Analog Input 3 Right                                                                                                                        |  |  |  |

| IN3L              | I                                                                                                           | Analog Input 3 Left                                                                                                                         |  |  |  |

| AVSS              | Р                                                                                                           | Analog Ground                                                                                                                               |  |  |  |

| AVSS1             | Р                                                                                                           | Analog Ground                                                                                                                               |  |  |  |

| AVSS3             | Р                                                                                                           | Analog Ground                                                                                                                               |  |  |  |

| AVSS2             | Р                                                                                                           | Analog Ground                                                                                                                               |  |  |  |

| DVSS              | Р                                                                                                           | Digital Ground                                                                                                                              |  |  |  |

|                   | VREF_SAR  IN1L/AUX1  IN1R/AUX2  IN4R  HPVSS_SENSE  LOR  SRVSS  SRVDD  IN3R  IN3L  AVSS  AVSS1  AVSS3  AVSS2 | NAME                                                                                                                                        |  |  |  |

|          | PIN           | T)/DE    | DECODURE                                                                                                                                                                                                                                                                                                                                             |

|----------|---------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BALL NO. | NAME          | TYPE     | DESCRIPTION                                                                                                                                                                                                                                                                                                                                          |

| E8       | SPK_V         | Р        | Class-D Output Stage Power Supply (Connect to SRVDD through a Resistor)                                                                                                                                                                                                                                                                              |

| E9       | SPKRP         | 0        | Right Channel P side Class-D Output                                                                                                                                                                                                                                                                                                                  |

| F1       | IN2L          | I        | Analog Input 2 Left                                                                                                                                                                                                                                                                                                                                  |

| F2       | IN2R          | I        | Analog Input 2 Right                                                                                                                                                                                                                                                                                                                                 |

| F3       | AVDD_18       | Р        | 1.8-V Analog Power Supply                                                                                                                                                                                                                                                                                                                            |

| F4       | DVSS          | Р        | Digital Ground                                                                                                                                                                                                                                                                                                                                       |

|          |               |          | Multi Function Digital Input 3                                                                                                                                                                                                                                                                                                                       |

|          |               |          | Primary: (SPI_SELECT = 1)                                                                                                                                                                                                                                                                                                                            |

| F5       | GPI3          | 1        | ADC Bit Clock Input for Audio Serial Data Bus 1, 2, or 3 (Six-Wire Audio Interface) ADC Word Clock Input for Audio Serial Data Bus 1, 2, or 3 (Six-Wire Audio Interface)                                                                                                                                                                             |

|          |               |          | Secondary: (SPI_SELECT = 0)                                                                                                                                                                                                                                                                                                                          |

|          |               |          | I <sup>2</sup> C Address Bit 1 (I2C_ADDR0, LSB)                                                                                                                                                                                                                                                                                                      |

|          |               |          | Multi Function Digital Input 2                                                                                                                                                                                                                                                                                                                       |

|          |               |          | Primary:                                                                                                                                                                                                                                                                                                                                             |

|          |               |          | General Purpose Input                                                                                                                                                                                                                                                                                                                                |

|          |               |          | Secondary:                                                                                                                                                                                                                                                                                                                                           |

| F6       | GPI2          | I        | Audio Serial Data Bus 1 Data Input Audio Serial Data Bus 1 Data Input (L2/R2 or L3/R3 or L4/R4) Digital Microphone Data Input General Clock Input Low-Frequency Clock Input ADC Word Clock Input for Audio Serial Data Bus 1, 2, or 3 (Six-Wire Audio Interface) ADC Bit Clock Input for Audio Serial Data Bus 1, 2, or 3 (Six-Wire Audio Interface) |

|          |               |          | Multi Function Digital Input 4                                                                                                                                                                                                                                                                                                                       |

| F7       | GPI4          | ı        | Primary: (SPI_SELECT = 1)  ADC Bit Clock Input for Audio Serial Data Bus 1, 2, or 3 (Six-Wire Audio Interface)  ADC Word Clock Input for Audio Serial Data Bus 1, 2, or 3 (Six-Wire Audio Interface)                                                                                                                                                 |

|          |               |          | Secondary: (SPI_SELECT = 0)                                                                                                                                                                                                                                                                                                                          |

| Го       | 10,400        |          | I <sup>2</sup> C Address Bit 2 (I2C_ADDR1, MSB)                                                                                                                                                                                                                                                                                                      |

| F8       | IOVSS         | Р        | Digital I/O Buffer Ground  Pattery Manitor Voltage Input                                                                                                                                                                                                                                                                                             |

| F9<br>G1 | VBAT<br>MCLK1 | l        | Battery Monitor Voltage Input  Master Clock Input 1                                                                                                                                                                                                                                                                                                  |

| GI       | IVICENT       | <u>'</u> | Primary:                                                                                                                                                                                                                                                                                                                                             |

| G2       | BCLK2         | I/O      | Audio Serial Data Bus 2 Bit Clock  Secondary:  Audio Serial Data Bus 1 Data Input (L3/R3) Audio Serial Data Bus 1 Data Output (L3/R3) General Purpose Input General Purpose Output General CLKOUT Output ADC MOD Clock Output SAR ADC Interrupt INT1 Output INT2 Output General Clock Input Low-Frequency Clock Input                                |

|          | PIN        | TVDE | DECODINE                                                                                                                                                                                                                                                                                                                                        |

|----------|------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BALL NO. | NAME       | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                     |

| G3       | DIN2       | I    | Primary:  Audio Serial Data Bus 2 Data Input  Secondary:  Digital Microphone Data Input Audio Serial Data Bus 1 Data Input (L2/R2) General Purpose Input Low-Frequency Clock Input                                                                                                                                                              |

| G4       | WCLK2      | I/O  | Primary:     Audio Serial Data Bus 2 Word Clock  Secondary:      Audio Serial Data Bus 1 Data Input (L4/R4)     Audio Serial Data Bus 1 Data Output (L4/R4)     General Purpose Input     General Purpose Output     CLKOUT Output     ADC MOD Clock Output     SAR ADC Interrupt     INT1 Output     INT2 Output     Low-Frequency Clock Input |

| G5       | WCLK3      | I/O  | Primary:  Audio Serial Data Bus 3 Word Clock Secondary:  General Purpose Output General Purpose Input Audio Serial Data Bus 1 Data Out (L4/R4) Low-Frequency Clock Input                                                                                                                                                                        |

| G6       | DIN3       | I    | Primary: Audio Serial Data Bus 3 Data Input Secondary: Audio Serial Data Bus 1 Data Input (L3/R3)                                                                                                                                                                                                                                               |

| G7       | SPI_SELECT | I    | Control Interface Select SPI_SELECT = '1': SPI Interface selected SPI_SELECT = '0': I <sup>2</sup> C Interface selected                                                                                                                                                                                                                         |

| G8       | RESET      | I    | Active Low Reset                                                                                                                                                                                                                                                                                                                                |

| G9       | MCLK2      | I    | Master Clock 2 Primary: Clock Input Secondary: Digital Microphone Data Input Audio Serial Data Bus 1 Data Input (L3/R3 or L4/R4) Low-Frequency Clock Input                                                                                                                                                                                      |

| H1       | BCLK1      | I/O  | Primary: Audio Serial Data Bus 1 Bit Clock Secondary: General Clock Input                                                                                                                                                                                                                                                                       |

|          | PIN   | TVDE | DECORPORA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------|-------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BALL NO. | NAME  | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| H2       | DOUT1 | 0    | Primary: Audio Serial Data Bus 1 Data Output Secondary:  Audio Serial Data Bus 1 Data Output (L1/R1) General Purpose Output CLKOUT Output SAR ADC Interrupt INT1 Output INT2 Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| H3       | IOVDD | Р    | Digital I/O Buffer Supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| H4       | SCL   | I/O  | I <sup>2</sup> C Interface Serial Clock (SPI_SELECT = 0) SPI interface mode chip-select signal (SPI_SELECT = 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| H5       | SDA   | I/O  | I <sup>2</sup> C interface mode serial data input (SPI_SELECT = 0) SPI interface mode serial data input (SPI_SELECT = 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| H6       | GPO1  | 0    | Multifunction Digital Output 1 Primary: (SPI_SELECT = 1) Serial Data Output Secondary: (SPI_SELECT = 0) General Purpose Output CLKOUT Output ADC MOD Clock Output SAR ADC Interrupt INT1 Output INT2 Output Audio Serial Data Bus 1 Data Output (L2/R2 or L3/R3 or L4/R4)  Primary: Audio Serial Data Bus 3 Bit Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| H7       | BCLK3 | I/O  | Secondary:  General Purpose Input General Purpose Output Low-Frequency Clock Input Audio Serial Data Bus 1 Data Output (L3/R3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Н8       | GPIO2 | I/O  | Multi Function Digital IO 2  Outputs:  General Purpose Output ADC MOD Clock Output For Digital Microphone CLKOUT Output SAR ADC Interrupt INT1 Output INT2 Output Audio Serial Data Bus 1 Data Output (L2/R2 or L3/R3 or L4/R4) Audio Serial Data Bus 1 Bit Clock Output ADC Word Clock Output for Audio Serial Data Bus 1, 2, or 3 (Six-Wire Audio Interface) ADC Bit Clock Output for Audio Serial Data Bus 1, 2, or 3 (Six-Wire Audio Interface) Inputs:  General Purpose Input Digital Microphone Data Input Audio Serial Data Bus 1 Data Input (L2/R2 or L3/R3 or L4/R4) Audio Serial Data Bus 1 Bit Clock Input General Clock Input Low-Frequency Clock Input ADC Word Clock Input for Audio Serial Data Bus 1, 2, or 3 (Six-Wire Audio Interface) ADC Bit Clock Input for Audio Serial Data Bus 1, 2, or 3 (Six-Wire Audio Interface) |

| H9       | IOVDD | Р    | Digital I/O Buffer Supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|          | PIN   |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------|-------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BALL NO. | NAME  | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| J1       | DIN1  | I    | Primary:  Audio Serial Data Bus 1 Data Input Secondary:  Audio Serial Data Bus 1 Data Input (L1/R1) General Clock Input Digital Microphone Data Input                                                                                                                                                                                                                                                                                              |

| J2       | WCLK1 | I/O  | Primary:  Audio Serial Data Bus 1 Word Clock Secondary:  Low-Frequency Clock Input General CLKOUT Output                                                                                                                                                                                                                                                                                                                                           |

| J3       | DVDD  | Р    | 1.8-V Digital Power Supply                                                                                                                                                                                                                                                                                                                                                                                                                         |

| J4       | IOVSS | Р    | Digital I/O Buffer Ground                                                                                                                                                                                                                                                                                                                                                                                                                          |

| J5       | GPI1  | I    | Multifunction Digital Input 1  Primary: (SPI_SELECT = 1)  SPI Serial Clock  Secondary: (SPI_SELECT = 0)  Digital Microphone Data Input Audio Serial Data Bus 1 Data Input (L2/R2 or L3/R3 or L4/R4)  General Clock Input Low-Frequency Clock Input General Purpose Input ADC Word Clock Input for Audio Serial Data Bus 1, 2, or 3 (Six-Wire Audio Interface)  ADC Bit Clock Input for Audio Serial Data Bus 1, 2, or 3 (Six-Wire Audio Interface) |

| J6       | DOUT2 | 0    | Primary: Audio Serial Data Bus 2 Data Output  Secondary:  General Purpose Output ADC MOD Clock Output SAR ADC Interrupt INT1 Output INT2 Output Audio Serial Data Bus 1 Data Output (L2/R2)                                                                                                                                                                                                                                                        |

| J7       | DOUT3 | 0    | Primary: Audio Serial Data Bus 3 Data Output Secondary: General Purpose Output Audio Serial Data Bus 1 Data Output (L2/R2 or L3/R3) Audio Serial Data Bus 1 Word Clock Output                                                                                                                                                                                                                                                                      |

|          | PIN   | TVDE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|----------|-------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| BALL NO. | NAME  | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| J8       | GPIO1 | I/O  | Multi Function Digital IO 1  Outputs:  General Purpose Output ADC MOD Clock Output CLKOUT Output SAR ADC Interrupt INT1 Output INT2 Output Audio Serial Data Bus 1 Data Output (L3/R3 or L4/R4) Audio Serial Data Bus 1 Word Clock Output ADC Word Clock Output for Audio Serial Data Bus 1, 2, or 3 (Six-Wire Audio Interface) ADC Bit Clock Output for Audio Serial Data Bus 1, 2, or 3 (Six-Wire Audio Interface)  Inputs:  General Purpose Input Digital Microphone Data Input Audio Serial Data Bus 1 Data Input (L3/R3 or L4/R4) Audio Serial Data Bus 1 Data Input (L3/R3 or L4/R4) Audio Serial Data Bus 1 Word Clock Input General Clock Input Low-Frequency Clock Input ADC Word Clock Input for Audio Serial Data Bus 1, 2, or 3 (Six-Wire Audio Interface) ADC Bit Clock Input for Audio Serial Data Bus 1, 2, or 3 (Six-Wire Audio Interface) |  |  |  |

| J9       | DVDD  | Р    | 1.8-V Digital Power Supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

## 8 Specifications

#### 8.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)

|                                                                                     | MIN         | MAX            | UNIT |

|-------------------------------------------------------------------------------------|-------------|----------------|------|

| AVDD1_18, AVDD2_18, AVDD4_18, AVDD_18 to AVSS1, AVSS2, AVSS4, AVSS respectively (2) | -0.3        | 2.2            | V    |

| AVDD3_33 to AVSS3 and RECVDD_33 to RECVSS                                           | -0.3        | 3.9            | V    |

| DVDD to DVSS                                                                        | -0.3        | 2.2            | V    |

| IOVDD to IOVSS                                                                      | -0.3        | 3.9            | V    |

| HVDD_18 to AVSS                                                                     | -0.3        | 2.2            | V    |

| CPVDD_18 to CPVSS                                                                   | -0.3        | 2.2            | V    |

| SLVDD to SLVSS, SRVDD to SRVSS, SPK_V to SRVSS <sup>(3)</sup>                       | -0.3        | 6              | V    |

| Digital Input voltage to ground                                                     | IOVSS - 0.3 | IOVDD + 0.3    | V    |

| Analog input voltage to ground                                                      | AVSS - 0.3  | AVDDx_18 + 0.3 | V    |

| VBAT                                                                                | -0.3        | 6              | V    |

| Operating temperature                                                               | -40         | 85             | °C   |

| Junction temperature (T <sub>J</sub> Max)                                           |             | 105            | °C   |

| Storage temperature, T <sub>stq</sub>                                               | -55         | 125            | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 8.2 ESD Ratings

|                    |                         |                                                                                | VALUE | UNIT |

|--------------------|-------------------------|--------------------------------------------------------------------------------|-------|------|

| \/                 | Floatroatatia diaaharaa | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)                         | ±2400 | .,   |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±1000 | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

# 8.3 Recommended Operating Conditions

|                                                |                            |                                                                                                |                               | MIN                 | NOM | MAX  | UNIT |

|------------------------------------------------|----------------------------|------------------------------------------------------------------------------------------------|-------------------------------|---------------------|-----|------|------|

| AVDD1_18,<br>AVDD2_18,<br>AVDD4_18,<br>AVDD_18 |                            | Referenced to AVSS1, AVS respectively <sup>(1)</sup> It is recommon these supplies to a single | ended to connect each         | 1.5                 | 1.8 | 1.95 |      |

| AVDD3_33,<br>RECVDD_33                         | Power Supply Voltage Range | teferenced to AVSS3 and RECVSS respectively                                                    |                               | 1.65 <sup>(2)</sup> | 3.3 | 3.6  | V    |

| IOVDD                                          |                            | Referenced to IOVSS <sup>(1)</sup>                                                             |                               | 1.1                 |     | 3.6  |      |

| DVDD <sup>(3)</sup>                            |                            | Referenced to DVSS <sup>(1)</sup>                                                              |                               | 1.26                | 1.8 | 1.95 |      |

| CPVDD_18                                       |                            | Referenced to CPVSS (1)                                                                        |                               | 1.26                | 1.8 | 1.95 |      |

| LIV/DD 40                                      | Power Supply Voltage Range | Referenced to AVSS <sup>(1)</sup>                                                              | Ground-centered Configuration | 1.5 <sup>(2)</sup>  | 1.8 | 1.95 | V    |

| HVDD_18                                        |                            | Referenced to AVSS***                                                                          | Unipolar<br>Configuration     | 1.65 <sup>(2)</sup> |     | 3.6  |      |

| SLVDD <sup>(1)</sup>                           | Power Supply Voltage Range | Referenced to SLVSS <sup>(1)</sup>                                                             |                               | 2.7                 |     | 5.5  | V    |

<sup>(1)</sup> All grounds on board are tied together, so they should not differ in voltage by more than 0.1 V max, for any combination of ground signals. AVDDx\_18 are within ±0.05 V of each other. SLVDD, SRVDD, and SPK\_V are within ±0.05 V of each other.

<sup>(2)</sup> TI recommends to keep all AVDDx\_18 supplies within ± 50 mV of each other.

<sup>(3)</sup> TI recommends to keep SLVDD, SRVDD, and SPK\_V supplies within ± 50 mV of each other.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

<sup>(2)</sup> Minimum voltage for HVDD\_18 and RECVDD\_33 should be greater than or equal to AVDD2\_18. Minimum voltage for AVDD3\_33 should be greater than or equal to AVDD1\_18 and AVDD2\_18.

<sup>(3)</sup> At DVDD values lower than 1.65V, the PLL does not function. Please see table in SLAU309, *Maximum TLV320AlC3262 Clock Frequencies* for details on maximum clock frequencies.

# **Recommended Operating Conditions (continued)**

|                                     |                                                    |                                                                                                                                                                             | MIN   | NOM | MAX      | UNIT  |

|-------------------------------------|----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|----------|-------|

| SRVDD <sup>(1)</sup>                | Power Supply Voltage Range                         | Referenced to SRVSS <sup>(1)</sup>                                                                                                                                          | 2.7   |     | 5.5      | V     |

| SPK_V <sup>(1)</sup>                | Power Supply Voltage Range                         | Referenced to SRVSS <sup>(1)</sup>                                                                                                                                          | 2.7   |     | 5.5      | ٧     |

| VREF_SAR                            | External voltage reference for SAR                 | Referenced to AVSS                                                                                                                                                          |       | 1.8 | AVDDx_18 | V     |

|                                     | PLL Input Frequency <sup>(4)</sup>                 | Clock divider uses fractional divide<br>(D > 0), P=1, PLL_CLKIN_DIV=1, DVDD ≥ 1.65 V<br>(Refer to table in SLAU309, <i>Maximum</i><br>TLV320AIC3262 Clock Frequencies)      | 10    |     | 20       | MHz   |

|                                     | FLL Input Frequency V                              | Clock divider uses integer divide<br>(D = 0), P=1, PLL_CLKIN_DIV=1, DVDD ≥ 1.65 V<br>(Refer to table in SLAU309, <i>Maximum</i><br><i>TLV320AIC3262 Clock Frequencies</i> ) | 0.512 |     | 20       | MHz   |

| MCLK                                | Magter Cleak Fraguency                             | MCLK; Master Clock Frequency; IOVDD ≥ 1.65 V                                                                                                                                |       |     | 50       | MHz   |

| IVICEK                              | Master Clock Frequency                             | MCLK; Master Clock Frequency; IOVDD ≥ 1.1 V                                                                                                                                 |       |     | 33       | IVITZ |

| SCL                                 | SCL Clock Frequency                                |                                                                                                                                                                             |       |     | 400      | kHz   |

| LOL, LOR                            | Stereo line output load resistance                 |                                                                                                                                                                             | 0.6   | 10  |          | kΩ    |

| HPL, HPR                            | Stereo Headphone Output<br>Load Resistance         | Single-ended configuration                                                                                                                                                  | 14.4  | 16  |          | Ω     |

| SPKLP-<br>SPKLM,<br>SPKRP-<br>SPKRM | Speaker Output Load<br>Resistance                  | Differential                                                                                                                                                                | 7.2   | 8   |          | Ω     |

| RECP-RECM                           | Receiver output resistance                         | Differential                                                                                                                                                                | 24.4  | 32  |          | Ω     |

| C <sub>IN</sub>                     | Charge Pump Input Capacitor (CPVDD to CPVSS Pins)  |                                                                                                                                                                             |       | 10  |          | μF    |

| Co                                  | Charge Pump Output<br>Capacitor (VNEG Pin)         | Type X7R                                                                                                                                                                    |       | 2.2 |          | μF    |

| C <sub>F</sub>                      | Charge Pump Flying Capacitor (CPFCP to CPFCM Pins) | Type X7R                                                                                                                                                                    |       | 2.2 |          | μF    |

| TOPR                                | Operating Temperature Range                        |                                                                                                                                                                             | -40   |     | 85       | °C    |

<sup>(4)</sup> The PLL Input Frequency refers to clock frequency after PLL\_CLKIN\_DIV divider. Frequencies higher than 20 MHz can be sent as an input to this PLL\_CLKIN\_DIV and reduced in frequency prior to input to the PLL.

#### 8.4 Thermal Information

|                      |                                              | TLV320AIC3262 |      |

|----------------------|----------------------------------------------|---------------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                | YZF (DSBGA)   | UNIT |

|                      |                                              | 81 PINS       |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 39.1          | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 0.1           | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 12.0          | °C/W |

| ΨЈТ                  | Junction-to-top characterization parameter   | 0.7           | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter | 11.5          | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

## 8.5 Electrical Characteristics, SAR ADC

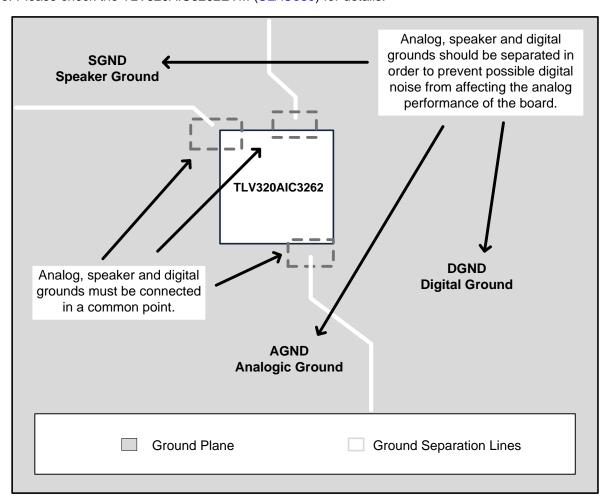

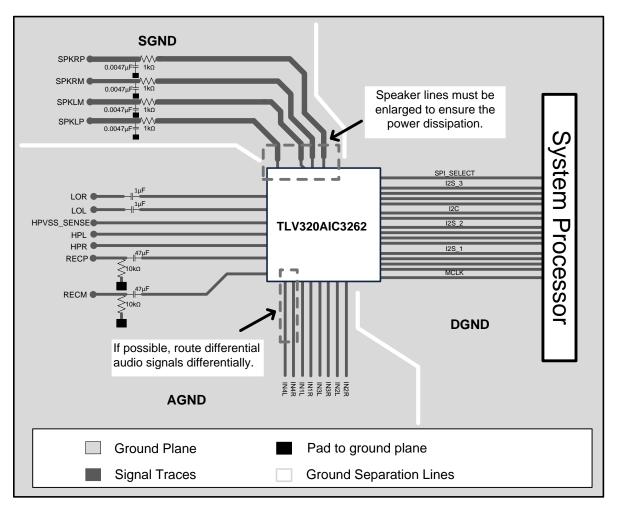

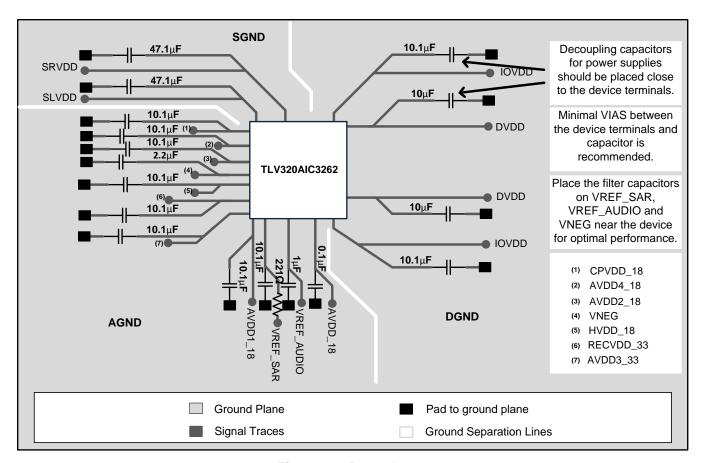

|               | PARAMETER                              | TEST CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | MIN  | TYP                                   | MAX      | UNIT          |