www.ti.com.cn

TXS4558

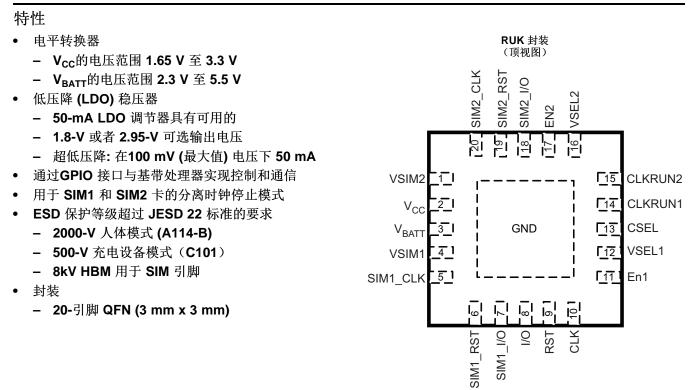

# 具有电平转换器和专用双LDO的双SIM卡电源

查询样品: TXS4558

NOTE: 裸露的中心散热焊盘必须电接地。

说明

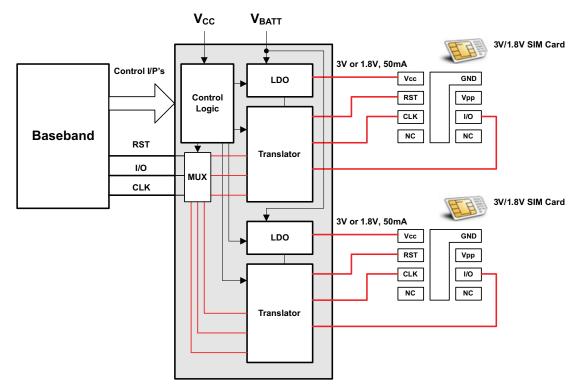

TXS4558 是一款完整的双电源待机智能身份模块 (SIM) 卡解决方案,用于将无线基带处理器与两个单独的 SIM 用 户卡相连,以存储移动手机应用程序的数据。这是一款定制器件,用于把单个 SIM/UICC 接口扩展至能够支持两个 SIM/UICC (通用集成芯片卡)。

该器件不但符合 ISO / IEC 智能卡接口要求,而且还支持 GSM 与 3G 移动标准。 它包含能够支持 Class B (2.95 V) 与 Class C (1.8 V) 接口的高速电平转换器、低压降 (LDO) 稳压器,可在 2.95 V Class B 与 1.8 V Class C 接口 之间选择输出电压。简单GPIO输入用于在两个SIM卡之间进行交换并使其进入不同模式。 电压电平转换器具有两 个电源电压引脚。 VCC 负责设定用于基带接口的基准,并可采用 1.65V 至 3.3V 的工作电压。 VSIM1 和 VSIM2 被设置为

1.8V 或 2.95V,各由一个独立的内部 LDO 稳压器供电。 集成型 LDO 可接受 2.3V 至 5.5V 的输入电池电压,并向B侧电路及外部 Class B 或 Class C SIM 卡输出高达 50mA 的电流。

此外,TXS4558 还根据 SIM 卡的 ISO 7816-3 规范为 SIM 卡引脚整合了关断定序功能。 该器件不但可为 SIM 引 脚提供 8 kV HBM 保护,而且还可为所有其它引脚提供标准 2kV HBM 保护。

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

## TXS4558

#### ZHCS377A-SEPTEMBER 2011-REVISED SEPTEMBER 2011

TEXAS INSTRUMENTS

www.ti.com.cn

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

#### ORDERING INFORMATION<sup>(1)</sup>

| T <sub>A</sub> | PACKAGE <sup>(2)</sup> |               | ORDERABLE PART NUMBER | TOP-SIDE MARKING |

|----------------|------------------------|---------------|-----------------------|------------------|

| –40°C to 85°C  | QFN – RUK              | Tape and reel | TXS4558RUKR           | ZTG              |

(1) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI web site at www.ti.com.

(2) Package drawings, thermal data, and symbolization are available at www.ti.com/packaging.

#### INTERFACING THE SIM CARD

#### **PIN FUNCTIONS**<sup>(1)</sup>

| NO. | NAME              | TYPE <sup>(2)</sup> | POWER DOMAIN      | DESCRIPTION                                                             |

|-----|-------------------|---------------------|-------------------|-------------------------------------------------------------------------|

| 1   | VSIM2             | 0                   | V <sub>BATT</sub> | 1.8 V/2.95 V supply voltage to SIM2                                     |

| 2   | V <sub>CC</sub>   | Р                   | —                 | 1.8-V power supply for device operation and I/O buffers toward baseband |

| 3   | V <sub>BATT</sub> | Р                   | —                 | Battery power supply                                                    |

| 4   | VSIM1             | 0                   | VBATT             | 1.8 V/2.95 V supply voltage to SIM1                                     |

| 5   | SIM1CLK           | 0                   | VSIM1             | SIM1 clock                                                              |

| 6   | SIM1RST           | 0                   | VSIM1             | SIM1 reset                                                              |

| 7   | SIM1I/O           | I/O                 | VSIM1             | SIM1 data                                                               |

| 8   | I/O               | I/O                 | V <sub>CC</sub>   | UICC/SIM data                                                           |

| 9   | RST               | I                   | V <sub>CC</sub>   | UICC/SIM reset from baseband                                            |

| 10  | CLK               | I                   | V <sub>CC</sub>   | UICC/SIM clock                                                          |

| 11  | EN1               | I                   | V <sub>CC</sub>   | Enable pin for SIM1 interface                                           |

| 12  | VSEL1             | I                   | V <sub>CC</sub>   | Select pin for 1.8V or 2.95V LDO1 output                                |

| 13  | CSEL              | Ι                   | V <sub>CC</sub>   | Channel select between SIM1 or SIM2                                     |

(1) Thermal Pad must be electrically connected to Ground Plane.

(2) G = Ground, I = Input, O = Output, P = Power

ZHCS377A - SEPTEMBER 2011 - REVISED SEPTEMBER 2011

www.ti.com.cn

## PIN FUNCTIONS<sup>(1)</sup> (continued)

| NO. | NAME    | TYPE <sup>(2)</sup> | POWER DOMAIN    | DESCRIPTION                              |

|-----|---------|---------------------|-----------------|------------------------------------------|

| 14  | CLKRUN1 | I                   | V <sub>CC</sub> | Select pin for SIM1 Clock stop mode      |

| 15  | CLKRUN2 | I                   | V <sub>CC</sub> | Select pin for SIM2 Clock stop mode      |

| 16  | VSEL2   | I                   | V <sub>CC</sub> | Select pin for 1.8V or 2.95V LDO2 output |

| 17  | EN2     | I                   | V <sub>CC</sub> | Enable pin for SIM2 interface            |

| 18  | SIM2I/O | I/O                 | VSIM2           | SIM2 data                                |

| 19  | SIM2RST | 0                   | VSIM2           | SIM2 reset                               |

| 20  | SIM2CLK | 0                   | VSIM2           | SIM2 clock                               |

#### **TRUTH TABLE**

| CSEL | VSEL1 | VSEL2 | SELECTED CARD | VSIM1  | VSIM2  |  |  |

|------|-------|-------|---------------|--------|--------|--|--|

| 0    | 0     | 0     | 1             | 1.8 V  | 1.8 V  |  |  |

| 0    | 0     | 1     | 1             | 1.8 V  | 2.95 V |  |  |

| 0    | 1     | 0     | 1             | 2.95 V | 1.8 V  |  |  |

| 0    | 1     | 1     | 1             | 2.95 V | 2.95 V |  |  |

| 1    | 0     | 0     | 2             | 1.8 V  | 1.8 V  |  |  |

| 1    | 0     | 1     | 2             | 1.8 V  | 2.95 V |  |  |

| 1    | 1     | 0     | 2             | 2.95 V | 1.8 V  |  |  |

| 1    | 1     | 1     | 2             | 2.95 V | 2.95 V |  |  |

### **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range (unless otherwise noted)

|                  |                                                                              |                            | MIN  | MAX | UNIT |

|------------------|------------------------------------------------------------------------------|----------------------------|------|-----|------|

| LEVE             | L TRANSLATOR                                                                 |                            | L.   |     |      |

| VCC              | Supply voltage range                                                         |                            | -0.3 | 4.0 | V    |

|                  |                                                                              | VCC-port                   | -0.5 | 4.6 |      |

| VI               | Input voltage range                                                          | VSIMx-port                 | -0.5 | 4.6 | V    |

|                  |                                                                              | Control inputs             | -0.5 | 4.6 |      |

|                  |                                                                              | VCC-port                   | -0.5 | 4.6 |      |

| Vo               | Voltage range applied to any output in the high-impedance or power-off state | VSIMx-port                 | -0.5 | 4.6 | V    |

|                  | power on state                                                               | Control inputs             | -0.5 | 4.6 |      |

|                  | Voltage range applied to any output in the high or low state                 | VCC-port                   | -0.5 | 4.6 |      |

| Vo               |                                                                              | VSIMx-port                 | -0.5 | 4.6 | V    |

|                  |                                                                              | Control inputs             | -0.5 | 4.6 |      |

| I <sub>IK</sub>  | Input clamp current                                                          | V <sub>1</sub> < 0         |      | -50 | mA   |

| I <sub>OK</sub>  | Output clamp current                                                         | V <sub>O</sub> < 0         |      | -50 | mA   |

| I <sub>O</sub>   | Continuous output current                                                    |                            | ±50  |     | mA   |

|                  | Continuous current through VCCA or GND                                       |                            | ±100 |     | mA   |

| T <sub>stg</sub> | Storage temperature range                                                    |                            | -65  | 150 | °C   |

| LDO              |                                                                              |                            |      |     |      |

| V <sub>BAT</sub> | Input voltage range                                                          |                            | -0.3 | 6   | V    |

| V <sub>OUT</sub> | Output voltage range                                                         |                            | -0.3 | 6   | V    |

| TJ               | Junction temperature range                                                   |                            | -55  | 150 | °C   |

| T <sub>stg</sub> | Storage temperature range                                                    |                            | -55  | 150 | °C   |

|                  | FSD roting (heat aids)                                                       | Human-Body Model (HBM)     |      | 2   | kV   |

|                  | ESD rating (host side)                                                       | Charged-Device Model (CDM) |      | 500 | V    |

ZHCS377A-SEPTEMBER 2011-REVISED SEPTEMBER 2011

## **RECOMMENDED OPERATING CONDITIONS**<sup>(1)</sup>

|                 |                                    |                                                   | MIN       | MAX       | UNIT |  |  |  |

|-----------------|------------------------------------|---------------------------------------------------|-----------|-----------|------|--|--|--|

| LEVEL           | LEVEL TRANSLATOR                   |                                                   |           |           |      |  |  |  |

| VCC             | Supply voltage                     |                                                   | 1.7       | 3.3       | V    |  |  |  |

| VIH             | High-level input voltage           | Applies to pins: EN1, EN2,RST, CLK, I/O, CLKRUN1, | VCC × 0.7 | 3.3       | V    |  |  |  |

| V <sub>IL</sub> | Low-level input voltage            | CLKRUN2, VSEL1, VSEL2, CSEL                       | 0         | VCC × 0.3 | V    |  |  |  |

| Δt/Δv           | Input transition rise or fa        |                                                   | 5         | ns/V      |      |  |  |  |

| T <sub>A</sub>  | Operating free-air temperature -40 |                                                   |           | 85        | °C   |  |  |  |

All unused data inputs of the device must be held at V<sub>CCI</sub> or GND to ensure proper device operation. Refer to the TI application report, Implications of Slow or Floating CMOS Inputs, literature number SCBA004.

## **ELECTRICAL CHARACTERISTICS — LEVEL TRANSLATOR**

over recommended operating free-air temperature range (unless otherwise noted)

| P                   | ARAMETER       | TEST CONDITIONS                                                    | VCC            | VSIM1                                | VSIM2                                | MIN                                 | TYP <sup>(1)</sup>                  | MAX      | UNIT       |          |   |

|---------------------|----------------|--------------------------------------------------------------------|----------------|--------------------------------------|--------------------------------------|-------------------------------------|-------------------------------------|----------|------------|----------|---|

|                     | SIM1_RST       | I <sub>OH</sub> = –100 μA, Push-Pull                               |                |                                      |                                      | VSIM1 × 0.8                         |                                     |          |            |          |   |

|                     | SIM1_CLK       | $I_{OH} = -100 \ \mu A$ , Push-Puli                                |                |                                      |                                      | VSIM1 × 0.8                         |                                     |          |            |          |   |

|                     | SIM1_I/O       | I <sub>OH</sub> = −10 μA, Open-Drain                               |                |                                      |                                      | VSIM1 × 0.8                         |                                     |          |            |          |   |

| V <sub>OH</sub>     | SIM2_RST       | I <sub>OH</sub> = –100 μA, Push-Pull                               | 1.7 V to 3.3 V | 1.8 V / 2.95 V,<br>(Supplied by LDO) | 1.8 V / 2.95 V,<br>(Supplied by LDO) | VSIM2 × 0.8                         |                                     |          | V          |          |   |

|                     | SIM2_CLK       | $I_{OH} = -100 \ \mu A$ , Push-Puli                                |                | (Supplied by EDO)                    | (oupplied by EDO)                    | VSIM2 × 0.8                         |                                     |          |            |          |   |

|                     | SIM2_I/O       | I <sub>OH</sub> = −10 μA, Open-Drain                               |                |                                      |                                      | VSIM2 × 0.8                         |                                     |          |            |          |   |

|                     | I/O            | I <sub>OH</sub> = −10 μA, Open-Drain                               |                |                                      |                                      | VCC × 0.8                           |                                     |          |            |          |   |

|                     | SIM1_RST       | L A mA Duck Dull                                                   |                |                                      |                                      |                                     | VSI                                 | M1 × 0.2 |            |          |   |

|                     | SIM1_CLK       | I <sub>OL</sub> = 1 mA, Push-Pull                                  |                |                                      |                                      |                                     | VSI                                 | M1 × 0.2 |            |          |   |

|                     | SIM1_I/O       | I <sub>OL</sub> = 1 mA, Open-Drain                                 | 1.7 V to 3.3 V | 1.7 V to 3.3 V                       | 1.7 V to 3.3 V                       |                                     |                                     |          |            | 0.3      |   |

| V <sub>OL</sub>     | SIM2_RST       |                                                                    |                |                                      |                                      | 1.8 V / 2.95 V<br>(Supplied by LDO) | 1.8 V / 2.95 V<br>(Supplied by LDO) |          | VSI        | M2 × 0.2 | V |

|                     | SIM2_CLK       | I <sub>OL</sub> = 1 mA, Push-Pull                                  |                | (Oupplied by EDO)                    | (Supplied by EDO)                    |                                     | VSI                                 | M2 × 0.2 |            |          |   |

|                     | SIM2_I/O       | I <sub>OL</sub> = 1 mA, Open-Drain                                 |                |                                      |                                      |                                     |                                     | 0.3      |            |          |   |

|                     | I/O            | I <sub>OL</sub> = 1 mA, Open-Drain                                 |                |                                      |                                      |                                     |                                     | 0.3      |            |          |   |

| I,                  | Control inputs | V <sub>I</sub> = EN1,EN2, CLKRUN1, CSEL,<br>CLKRUN2, VSEL1, VSEL2, | 1.7 V to 3.3 V | 1.8 V / 2.95 V<br>(Supplied by LDO)  | 1.8 V / 2.95 V<br>(Supplied by LDO)  |                                     |                                     | ±1       | μA         |          |   |

| I <sub>CC I/O</sub> |                | $V_{I}=V_{CCI},\ I_{O}=0$                                          | 1.7 V to 3.3 V | 1.8 V / 2.95 V<br>(Supplied by LDO)  | 1.8 V / 2.95 V<br>(Supplied by LDO)  |                                     |                                     | ±5       | μA         |          |   |

| <u> </u>            | SIM_I/O port   |                                                                    |                |                                      |                                      |                                     | 8                                   |          | ~ <b>F</b> |          |   |

| C <sub>io</sub>     | VSIMx port     |                                                                    |                |                                      |                                      |                                     | 8                                   |          | pF         |          |   |

| Ci                  | Control inputs | V <sub>I</sub> = VCC or GND                                        |                |                                      |                                      |                                     | 4                                   |          | pF         |          |   |

(1) All typical values are at  $T_A = 25^{\circ}C$ .

### LDO ELECTRICAL CHARACTERISTICS

|                                                                                                             | PARAMETER                      | TEST CONDITIONS                                                              |                        | MIN  | TYP <sup>(1)</sup> | MAX  | UNIT |

|-------------------------------------------------------------------------------------------------------------|--------------------------------|------------------------------------------------------------------------------|------------------------|------|--------------------|------|------|

| VBAT                                                                                                        | Input voltage                  |                                                                              |                        | 2.3  |                    | 5.5  | V    |

| V                                                                                                           | Output veltage                 | Class-B Mode , 0 mA < I <sub>SIM1,2</sub> < 50 mA                            |                        | 2.85 | 2.95               | 3.05 | V    |

| V <sub>SIM1,2</sub>                                                                                         | Output voltage                 | Class-C Mode , 0 mA < $I_{SIM1,2}$ < 50 mA                                   |                        | 1.7  | 1.8                | 1.9  | v    |

| V <sub>DO</sub>                                                                                             | Dropout voltage                | I <sub>OUT</sub> = 50 mA                                                     |                        |      |                    | 100  | mV   |

|                                                                                                             | Operating ourrent              | $V_{SIM1} = 2.95 \text{ V}, V_{SIM2} = 0, \text{ ISIM1} = 0 \ \mu\text{A}$   |                        |      | 40                 | 50   |      |

| I <sub>VBAT</sub> Operating current                                                                         |                                | $V_{SIM1} = 1.8 \text{ V}, V_{SIM2} = 0, I_{SIM1} = 0 \ \mu\text{A}$         |                        |      | 40                 | 50   | μA   |

| I <sub>SHDN</sub>                                                                                           | Shutdown current (IGND)        | $V_{ENx} \le 0.4 \text{ V}, (\text{VSIMx} + V_{DO}) \le \text{VBAT} \le 5.5$ | V, $T_J = 85^{\circ}C$ |      |                    | 1    | μA   |

| I <sub>OUT(SC)</sub>                                                                                        | Short-circuit current          | $R_L = 0 \Omega$                                                             |                        |      | 145                |      | mA   |

| C <sub>OUT</sub>                                                                                            | Output Capacitor               |                                                                              |                        |      | 1                  |      | μF   |

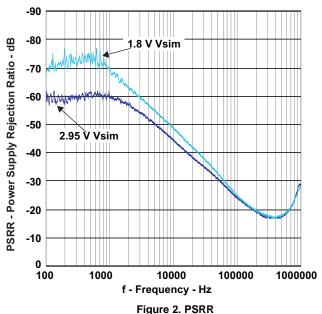

|                                                                                                             | Devues events action action    | V <sub>BAT</sub> = 3.15 V, V <sub>SIM1.2</sub> = 1.8 V or 2.95 V,            | f = 1 kHz              | 50   |                    |      |      |

| PSRR Power-supply rejection ratio                                                                           |                                | $C_{OUT} = 1 \ \mu F$ , $I_{OUT} = 10 \ mA$                                  | f = 10 kHz             | 40   |                    |      | dB   |

| $T_{STR}$ V <sub>SIM1,2</sub> Start-up time V <sub>SIM1,2</sub> = 1.8 V or 3 V, I <sub>OUT</sub> = 50 mA, C |                                | $V_{SIM1,2}$ = 1.8 V or 3 V, $I_{OUT}$ = 50 mA, $C_{OUT}$                    | = 1 µF                 |      |                    | 400  | μS   |

| TJ                                                                                                          | Operating junction temperature |                                                                              |                        | -40  |                    | 125  | °C   |

(1) All typical values are at  $T_A = 25^{\circ}C$ .

4

www.ti.com.cn

www.ti.com.cn

#### ZHCS377A - SEPTEMBER 2011 - REVISED SEPTEMBER 2011

### **GENERAL ELECTRICAL CHARACTERISTICS**

|                    | PARAMETER         | TEST CONDITIONS                                                                                           | MIN | TYP | MAX | UNIT |

|--------------------|-------------------|-----------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| R <sub>I/OPU</sub> | I/O pull-up       |                                                                                                           | 16  | 20  | 24  | kΩ   |

| R <sub>SIMPU</sub> | SIM_I/O pull-up   | SIM enabled and selected with CSEL                                                                        | 7.4 | 8.0 | 8.7 | kΩ   |

| R <sub>SIMPD</sub> | SIM_I/O pull-down | Active pull-downs are connected to the VSIM regulator output to the SIM_CLK, SIM_RST, SIM_I/O when EN = 0 |     |     | 2   | kΩ   |

## SWITCHING CHARACTERISTICS – VSIMx = 1.8 V or 2.95 V Supplied by Internal LDO

over recommended operating free-air temperature range (unless otherwise noted)

| DADAMETED        |           | TEST CONDITIONS        | VCC = 1.8 V ± | VCC = 1.8 V ± 0.15 V |      |  |

|------------------|-----------|------------------------|---------------|----------------------|------|--|

| r                | PARAMETER | TEST CONDITIONS        | MIN           | MAX                  | UNIT |  |

| t <sub>rA</sub>  | I/O       |                        |               | 1                    | μs   |  |

|                  | SIMx_RST  |                        |               | 1                    | μs   |  |

| t <sub>rB</sub>  | SIMx_CLK  |                        |               | 50                   | ns   |  |

|                  | SIMx_I/O  | C <sub>L</sub> = 50 pF |               | 100                  | ns   |  |

| f <sub>max</sub> | SIMx_CLK  |                        |               | 25                   | MHz  |  |

| Duty Cycle       | SIMx_CLK  |                        | 40%           | 60%                  |      |  |

### **OPERATING CHARACTERISTICS**

$T_A = 25^{\circ}C, V_{SIMx} = 1.8 V$

|                                | PA                    | ARAMETER                             | TEST CONDITIONS                                | ТҮР  | UNIT |

|--------------------------------|-----------------------|--------------------------------------|------------------------------------------------|------|------|

|                                | Class C (CLK,<br>RST) | VCC-port input, VSIMx-port<br>output |                                                | 12.7 | ~    |

| <b>c</b> (1)                   | Class B (CLK,<br>RST) | VCC-port input, VSIMx-port<br>output | $C_{L} = 0$                                    | 15.4 | pF   |

| C <sub>pd</sub> <sup>(1)</sup> | CLASS C (IO)          | VCC-port input, VSIMx-port<br>output | $f = 5 \text{ MHz}$ $t_r = t_f = 1 \text{ ns}$ | 10.8 |      |

|                                | CLASS B (IO)          | VCC-port input, VSIMx-port<br>output |                                                | 20.3 | pF   |

(1) Power dissipation capacitance per transceiver

ZHCS377A - SEPTEMBER 2011 - REVISED SEPTEMBER 2011

www.ti.com.cn

## **PIN FUNCTION**

| PIN NAME           | PIN NUMBER | PIN FUNCTION                                                                                                                                                                                                                                                                                                                                                                             |

|--------------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VCC                | 2          | Power supply and voltage reference for device operation and I/O buffers toward baseband.                                                                                                                                                                                                                                                                                                 |

| VBATT              | 3          | This is the battery power supply for the TXS4558.                                                                                                                                                                                                                                                                                                                                        |

| VSIM1, VSIM2       | 1,4        | 1.8 V/2.95 V supply voltage for the respective SIM1 and SIM2. These outputs are activated through the EN1 and EN2 pins and set to be 1.8V or 2.95V through VSEL1 and VSEL2.                                                                                                                                                                                                              |

| SIMCLK, SIM2CLK    | 5, 20      | These are voltage level shifted CLK signals for connection to SIM1 and SIM2.<br>Functionality while the corresponding SIM is not selected via CSEL is controlled by<br>CLKRUN1 and CLKRUN2 control pins.                                                                                                                                                                                 |

| SIM1RST, SIM2RST   | 6, 19      | These are voltage level shifted RST signals for connection to SIM1 and SIM2. Their output level when de-selected is latched at the last state.                                                                                                                                                                                                                                           |

| SIM1IO, SIM2IO     | 7, 18      | These are voltage level shifted IO signals for connection to SIM1 and SIM2. These are bi-directional data signals.                                                                                                                                                                                                                                                                       |

| Ю                  | 8          | Microcontroller side data IO pin. The IO pin provides the bidirectional communication path to the SIM cards. The SIMxIO communicating with IO is selected by CSEL.                                                                                                                                                                                                                       |

| RST                | 9          | Microcontroller side reset RST pin input. RST provides signals directly to the selected SIM SIMxRST. When a SIM interface is deselected with CSEL, the last RST value is held at the SIMxRST.                                                                                                                                                                                            |

| CLK                | 10         | The CLK pin supplies the clock signal to the cards. It is level shifted and transmitted directly to the SIMxCLK pin of the selected card. If CLKRUNx is HIGH, the clock signal will be transmitted to the SIMxCLK pin, regardless of whether that card is selected.                                                                                                                      |

| EN1, EN2           | 11, 17     | EN1 and EN2 enable and disable the power supply to SIM1 and SIM2, and the corresponding interface.                                                                                                                                                                                                                                                                                       |

| VSEL1, VSEL2       | 12, 16     | These pins set the VSIM1 and VSIM2 voltages and the corresponding interface IO voltages. When VSELx is low, VSIMx is 1.8V. When VSELx is high, VSIMx is 2.95V.                                                                                                                                                                                                                           |

| CSEL               | 13         | CSEL selects which SIM is activated and communicates with the baseband. When CSEL is low, SIM1 is active. When CSEL is high, SIM2 is active.                                                                                                                                                                                                                                             |

| CLKRUN1, CLKRUN2   | 14, 15     | The CLKRUN1 and CLKRUN2 control the functionality of the SIM1CLK and SIM2CLK pins when their corresponding SIM cards are deselected using CSEL. When CLKRUNx is high, the CLK signal is transmitted to the corresponding SIMxCLK, even when the card is deselected with CSEL. When CLKRUNx is low, the SIMxCLK signal is brought low when the corresponding SIM is deselected with CSEL. |

| Exposed Center Pad | 21         | This center pad must be connected to ground.                                                                                                                                                                                                                                                                                                                                             |

|                    | 1          | · · · ·                                                                                                                                                                                                                                                                                                                                                                                  |

#### **OPERATION**

#### Clock Run Mode

SIMS have varying requirements for the SIM CLK. Using CLKRUN, the user can decide if the SIMxCLK pin continuously transmits the CLK signal, or is brought low when the SIM is deselected with CSEL. If CLKRUNx is LOW, the SIMxCLK is brought LOW two clock cycles after the SIMx is deselected with CSEL. If SIMxCLK is high, the CLK transmits to the SIMxCLK, even if the SIMx is deselected with CSEL.

#### CSEL

When a channel is deselected using the CSEL pin, the SIMxRST state is latched, the SIMxIO becomes high impedance and SIMxCLK function is dependent on CLKRUNx.

#### **Operation Activation/Deactivation**

When the EN1, EN2 pin is brought high, the device performs the activation sequence for the corresponding SIM interface. Each SIM interface is activated independently based on its EN IO.

#### Activation Sequence

- 1. The device holds SIMxIO, SIMxCLK and SIMxRST low.

- 2. VSIMx is activated and powered.

- 3. The device waits for the VSIMx output to reach the correct voltage. Once this voltage is reached, SIMxIO, and SIMxRST are enabled.

- 4. The SIMxCLK is activated on the 2nd rising edge after the SIMxIO is enabled.

When the ENx pin is brought low, the device performs the deactivation sequence for the corresponding SIM interface. Deactivation Sequence,

#### Deactivation Sequence

- 1. SIMxRST is deactivated and set low.

- 2. Two clock cycles after EN is brought LOW, the SIMxCLK is disabled and brought LOW. If the CLK is not active, SIMxCLK is disabled and brought low approximately 9us after ENx is brought low.

- 3. Approximately 9us after the ENx is brought LOW, SIMxIO is disabled and set LOW.

- 4. After SIMxIO is brought LOW, the VSIMx is deactivated and unpowered.

ZHCS377A-SEPTEMBER 2011-REVISED SEPTEMBER 2011

www.ti.com.cn

#### **APPLICATION INFORMATION**

The LDO's included on the TXS4558 achieve ultra-wide bandwidth and high loop gain, resulting in extremely high PSRR at very low headroom ( $V_{BAT} - V_{SIM1/2}$ ). The TXS4558 provides fixed regulation at 1.8V or 2.95V. Low noise, GPIO enable and low ground pin current make it ideal for portable applications. The device offers current limit and thermal protection, and is fully specified from -40°C to 125°C.

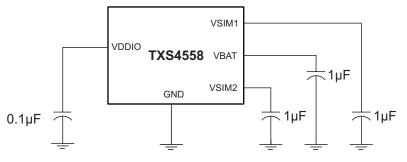

Figure 1. Typical Application Circuit for TXS4558

#### **Input and Output Capacitor Requirements**

It is good analog design practice to connect a 1.0 µF low equivalent series resistance (ESR) capacitor across the input supply (VBAT) near the regulator. Also, a 0.1µF is required for the logic core supply (VCC).

This capacitor will counteract reactive input sources and improve transient response, noise rejection, and ripple rejection. A higher-value capacitor may be necessary if large, fast rise-time load transients are anticipated or if the device is located several inches from the power source. The LDO's are designed to be stable with standard ceramic capacitors of values 1.0  $\mu$ F or larger. X5R- and X7R-type capacitors are best because they have minimal variation in value and ESR over temperature. Maximum ESR should be <1.0  $\Omega$ .

### Output Noise

In most LDO's, the bandgap is the dominant noise source. To improve ac performance such as PSRR, output noise, and transient response, it is recommended that the board be designed with separate ground planes for VIN and VOUT, with each ground plane connected only at the GND pin of the device. In addition, the ground connection for the bypass capacitor should connect directly to the GND pin of the device.

#### Internal Curent Limit

The TXS4558 internal current limit helps protect the regulator during fault conditions. During current limit, the output sources a fixed amount of current that is largely independent of output voltage. For reliable operation, the device should not be operated in a current limit state for extended periods of time.

The PMOS pass element in the TXS4558 has a built-in body diode that conducts current when the voltage at VSIM1/2 exceeds the voltage at VBAT. This current is not limited, so if extended reverse voltage operation is anticipated, external limiting may be appropriate.

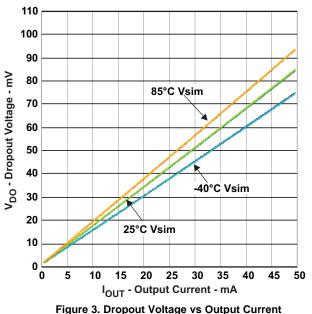

#### **Dropout Voltage**

The TXS4558 uses a PMOS pass transistor to achieve low dropout. When  $(V_{BAT} - V_{SIM1/2})$  is less than the dropout voltage  $(V_{DO})$ , the PMOS pass device is in its linear region of operation and the input-to-output resistance is the  $R_{DS(ON)}$  of the PMOS pass element.  $V_{DO}$  will approximately scale with output current because the PMOS device behaves like a resistor in dropout.

#### Startup

The TXS4558 uses a quick-start circuit which allows the combination of very low output noise and fast start-up times.

#### www.ti.com.cn

#### **Transient Response**

As with any regulator, increasing the size of the output capacitor reduces over/undershoot magnitude but increases duration of the transient response.

#### Minimum Load

The TXS4558 is stable and well-behaved with no output load. Traditional PMOS LDO regulators suffer from lower loop gain at very light output loads. The TXS4558 employs an innovative low-current mode circuit to increase loop gain under very light or no-load conditions, resulting in improved output voltage regulation performance down to zero output current.

#### THERMAL INFORMATION

#### **Thermal Protection**

Thermal protection disables the output when the junction temperature rises to approximately +160°C, allowing the device to cool. When the junction temperature cools to approximately +140°C the output circuitry is again enabled. Depending on power dissipation, thermal resistance, and ambient temperature, the thermal protection circuit may cycle on and off. This cycling limits the dissipation of the regulator, protecting it from damage because of overheating.

Any tendency to activate the thermal protection circuit indicates excessive power dissipation or an inadequate heat sink. For reliable operation, junction temperature should be limited to +125°C maximum. To estimate the margin of safety in a complete design (including heat sink), increase the ambient temperature until the thermal protection is triggered; use worst-case loads and signal conditions. For good reliability, thermal protection should trigger at least +35°C above the maximum expected ambient condition of your particular application. This configuration produces a worst-case junction temperature of 125°C at the highest expected ambient temperature and worst-case load.

The internal protection circuitry of the TXS4558 has been designed to protect against overload conditions. It was not intended to replace proper heat sinking. Continuously running the TXS4558 into thermal shutdown will degrade device reliability.

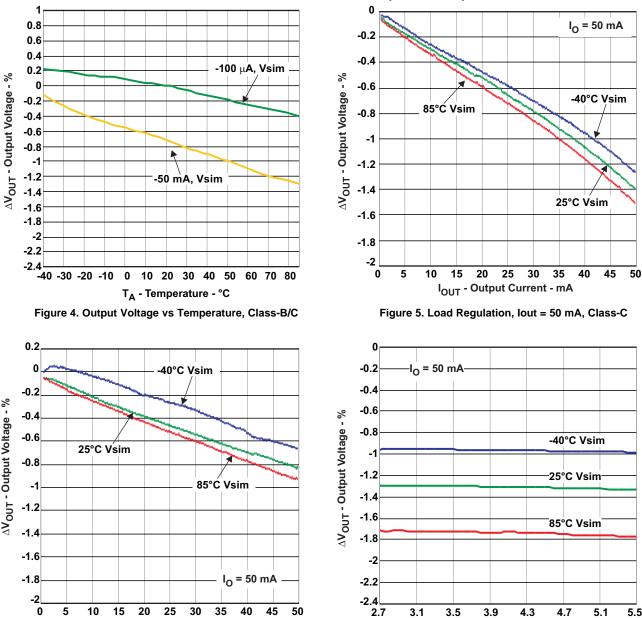

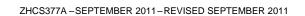

#### **TYPICAL CHARACTERISTICS**

Figure 6. Load Regulation, lout = 50 mA, Class-B

30 35 40 45 50

20 25

I<sub>OUT</sub> - Output Current - mA

Figure 7. Line Regulation, lout = 50 mA, Class-C

V<sub>BAT</sub> - V

4.3

4.7

5.1

5.5

3.9

3.1

3.5

∆V<sub>OUT</sub> - Output Voltage - %

0 5 10 15 EXAS **STRUMENTS**

www.ti.com.cn

### PACKAGING INFORMATION

| Orderable Device | Status<br>(1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan<br>(2) | Lead finish/<br>Ball material | MSL Peak Temp<br>(3) | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|---------------|--------------|--------------------|------|----------------|-----------------|-------------------------------|----------------------|--------------|-------------------------|---------|

| TXS4558RUKR      | ACTIVE        | WQFN         | RUK                | 20   | 3000           | RoHS & Green    | NIPDAU                        | Level-1-260C-UNLIM   | -40 to 85    | ZTG                     | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

**LIFEBUY:** TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

**RoHS Exempt:** TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

<sup>(5)</sup> Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

<sup>(6)</sup> Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

## PACKAGE MATERIALS INFORMATION

www.ti.com

Texas Instruments

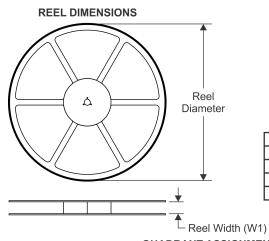

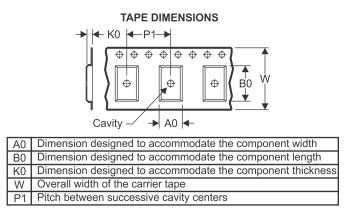

### TAPE AND REEL INFORMATION

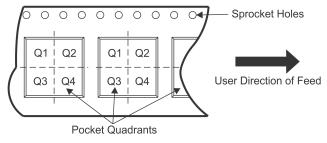

### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| *All dimensions | are | nominal |

|-----------------|-----|---------|

|-----------------|-----|---------|

| Device      | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| TXS4558RUKR | WQFN            | RUK                | 20 | 3000 | 330.0                    | 12.4                     | 3.3        | 3.3        | 1.1        | 8.0        | 12.0      | Q2               |

TEXAS INSTRUMENTS

www.ti.com

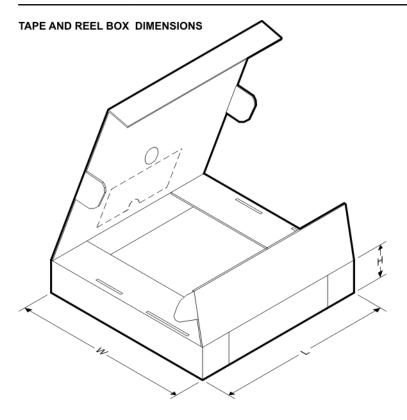

## PACKAGE MATERIALS INFORMATION

26-Jan-2013

\*All dimensions are nominal

| Device      | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TXS4558RUKR | WQFN         | RUK             | 20   | 3000 | 367.0       | 367.0      | 35.0        |

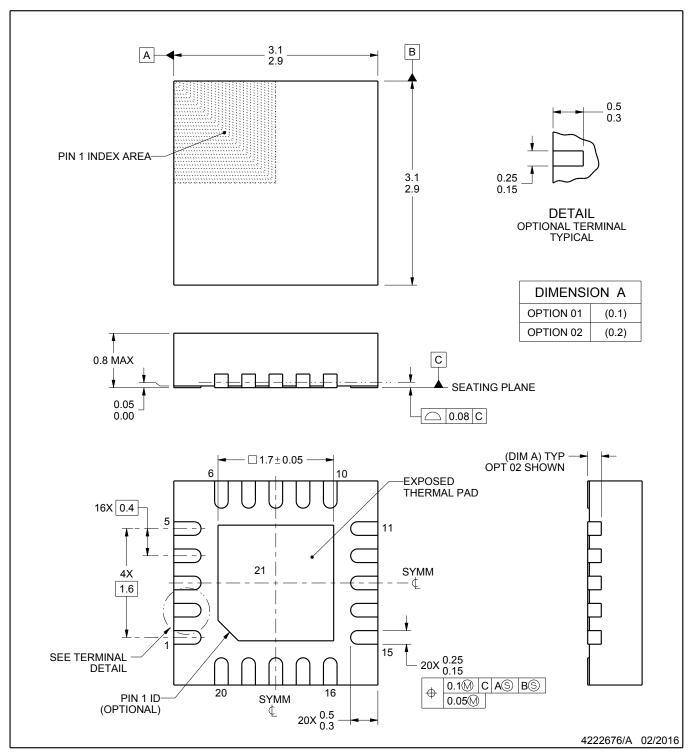

## **RUK0020B**

## **PACKAGE OUTLINE**

## WQFN - 0.8 mm max height

PLASTIC QUAD FLATPACK - NO LEAD

#### NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M. 2. This drawing is subject to change without notice.

- 3. The package thermal pad must be soldered to the printed circuit board for thermal and mechanical performance.

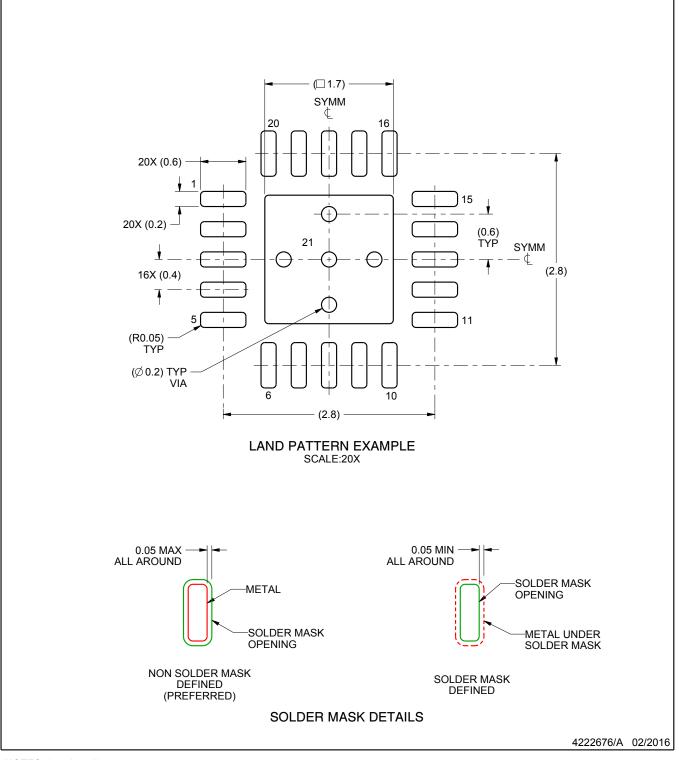

## **RUK0020B**

## **EXAMPLE BOARD LAYOUT**

## WQFN - 0.8 mm max height

PLASTIC QUAD FLATPACK - NO LEAD

NOTES: (continued)

4. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 (www.ti.com/lit/slua271).

Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

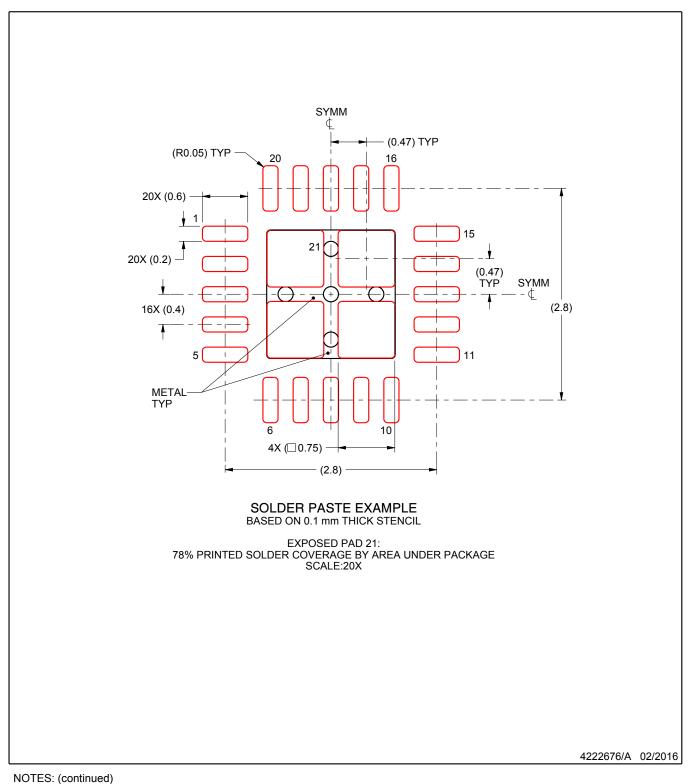

## **RUK0020B**

## **EXAMPLE STENCIL DESIGN**

## WQFN - 0.8 mm max height

PLASTIC QUAD FLATPACK - NO LEAD

6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

#### 重要声明和免责声明

TI"按原样"提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源, 不保证没有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、某特定用途方面的适用性或不侵犯任何第三方知识产权的暗示担 保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验 证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他功能安全、信息安全、监管或其他要求。

这些资源如有变更,恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的应用。严禁对这些资源进行其他复制或展示。 您无权使用任何其他 TI 知识产权或任何第三方知识产权。您应全额赔偿因在这些资源的使用中对 TI 及其代表造成的任何索赔、损害、成 本、损失和债务,TI 对此概不负责。

TI 提供的产品受 TI 的销售条款或 ti.com 上其他适用条款/TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

邮寄地址:Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022,德州仪器 (TI) 公司